# No. AN9741 July 1997

# Intersil

# **Basic DACs for Electronic Engineers**

Author: Ronald Mancini

### Why and Where are DACs Used?

The name is digital-to-analog converter, and the function of a DAC, as the name implies, is to convert digital signals into analog signals. Digital data is present at the output (and input) of digital systems (microprocessors are a subset of digital systems), and that data must be converted into an analog signal so that "real world" devices can use it. The "real world" interface is comprised of sensors and actuators; devices which must be controlled by an analog signal much like the analog signal found at the DAC output. Thus, DACs will be found at the interface between the digital system's output and the analog system's input.

The input registers of most DACs are flip-flops which act as a memory as long as the circuit doesn't lose power; hence, the DAC can fulfill the important analog memory function. The reference input to a control system, power supply (a specialized control system), or almost any other feedback system can be made from a reference diode and some passive components. This type of reference has memory, but it is not changeable without a hardware modification, so it is not used in systems that require frequent reference input changes (pin drivers, programmable power supplies, and a host of other electronic machines). A DAC is often the component of choice for an analog system that requires a stable but programmable reference input because the DAC is stable, it has excellent resolution, it has memory, and it is digitally programmable.

The DAC has the ability to multiply (this will be shown later). This property enables the DAC to multiply an analog signal by a digital number; and this capability is often employed to configure AGC circuits, digitally controlled op amps, system calibration functions, and waveform generators.

The DAC is a basic building block in electronic design; it serves as a digital-to-analog interface, as an analog memory, and as a multiplier, so we will study it in detail.

## **Binary Number Theory**

Digital engineers familiar with binary number systems may choose to skip this section. The decimal number system that is so familiar to us is based on the number 10, so it is called the base 10 number system. The base ten is used because we have 10 fingers on our hands, so we learn to count to ten using our fingers. The decimal number 206 is constructed in the base 10 system as shown below:

$$206 = 2(10^2) + 0(10^1) + 6(10^0)$$

(EQ. 1)

Notice that 206, in the decimal number system, is made up from three sums: each sum is based on a power of 10, and each sum requires the proper multiplier. The decimal number system has 10 integers, 0 through 9, thus, it can express large numbers with a few digits; i.e., any number from 0 to 9 can be expressed with a single digit, and any number up to 99 can be expressed with only two digits. The binary number system, which is used for digital work, has two integers, 0 and 1, so it needs many more digits to express the same number. The binary number system is used for digital computations because present day digital circuits have two easily manufactured stable states, on and off. If digital circuits had three easily manufacturable stable states, computers would use a tertiary or base 3 number system. The decimal number 206 is expressed in binary below.

$$206 = 1(2^{7}) + 1(2^{6}) + 0(2^{5}) + 0(2^{4}) +$$

$$1(2^{3}) + 1(2^{2}) + 1(2^{1}) + 0(2^{0})$$

(EQ. 2)

or

206 = 128 + 64 + 8 + 4 + 2 (EQ. 3)

Extracting the digit multipliers or "bits" from Equation 2 yields the binary equivalent of 206 as 11001110. It requires 8 digits to express 206 in binary as opposed to 3 digits in decimal. This does not make the decimal number system more powerful than the binary system, but the binary number system will require more electronic circuits to process the data. Because binary digital circuits are so much more simple than decimal digital circuits would be, digital math is done in binary or some form of binary such as octal or hexadecimal.

DAC math is just a little more complicated than this because the output of a DAC must range between zero and one. The DAC acts much like an attenuator because it does not have an internal amplifier, so fractional binary numbers are used for DAC math. Fractional binary numbers are expressed as shown below.

$$0.90625 = 1(2^{-1}) + 1(2^{-2}) + 1(2^{-3}) + 0(2^{-4}) + 1(2^{-5})$$

(EQ. 4)

or

$$0.90625 = 0.5 + 0.25 + 0.125 + 0.0 + 0.03125$$

(EQ. 5)

The resolution of a digital system is mathematically expressed as  $2^{n}$  where n is the number of bits. This is the maximum number of states that can exist in that system, so if zero is to be a number in the system, the largest number in the system is one bit less than full scale or  $1-2^{-n}$ . In a 6-bit fractional number system the smallest bit (called the LSB) is  $2^{-6}$  and the largest number is then  $1-2^{-n}$ . In a 6-bit system the largest number that can be represented is  $1-2^{-6} = 0.984375$ . The Equation for the digital portion of a DAC is given below:

$$D = \Sigma \ 1 - 2^{-n}, \ n = 0, \ 1, \ 2, \ 3, \ \dots$$

(EQ. 6)

#### **Basic DAC Theory**

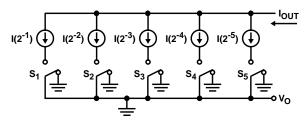

The simplest form of a DAC is shown in Figure 1; it is a collection of switched current sources where each current source is switched between ground or the output. The current sources are fractionally binaurally weighted, and the output current is the sum of the currents flowing into the output. Each current source has it's own bit switch,  $S_n$ , and the bit switch determines if the bit current flows into ground or the output. It is common practice to let  $S_n = 1$  represent a bit current flowing into the output, while  $S_n = 0$  represents a bit current flowing into ground.

FIGURE 1. SIMPLEST FORM OF A DAC

Equation 7 shown below includes Equation 6, although D is expressed in terms of the bit switches.

$$I_{OUT} = I_{DAC} \left\{ S_1(2^{-1}) + S_2(2^{-2}) + S_3(2^{-3}) + \dots S_n(2^{-n}) \right\}$$

(EQ. 7)

$I_{DAC}$  is the maximum current that the DAC can put out, and it is sometimes called the reference or DAC current. If the following settings are used for the bit switches:  $S_1 = 1$ ,  $S_2 = 1$ ,  $S_3 = 1$ ,  $S_4 = 0$ , S = 1, then;

$$I_{OUT} = I_{DAC} (1/2 + 1/4 + 1/8 + 0 + 1/32) = I_{DAC} (0.90625)$$

(EQ. 8)

Equation 8 illustrates the multiplying property of the DAC; the output current is the product of the sum-of-the-bit currents multiplied by the DAC reference current. The DC output states of the DAC are discrete steps, each of which is separated by a bit current. When the DAC is used in a DC application, such as a power supply reference, the smallest change that can be made in the reference is one bit times the DAC reference current. For an eight bit DAC with a 10mA reference current, the smallest current step is  $2^{-8}(10) =$ 0.0390625mA. The largest output current for this DAC is  $(1-2^{-8})(10))$  mA = (1 - 0.00390625(10))mA = 9.9609375mA, and the smallest DAC output current is  $(1-2^{-0})(10)$ mA = 0. Many DACs must process AC signals, and because of the DAC functions in discrete steps, the output current will change in discrete steps. When the DAC output is viewed on an oscilloscope the discrete bit steps are obvious, and these steps introduce high frequency noise into the AC signal. A smooth continuous output current is more desirable because it does not contain the DAC noise. Using the DAC at the highest possible clock frequency causes the discrete steps to be very high frequency, so they can be reduced to an acceptable level with a filter.

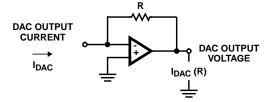

Many circuits, especially video and similar high frequency circuits, use the DAC output current directly, but there are many circuits which need a voltage output from the DAC. Figure 2 shows a popular circuit which is employed to convert the output current to voltage. The DAC current flows into the summing node of an op amp, and if the op amp follows the ideal op amp Equation, the resulting op amp out voltage is  $V_{OUT} = I_{DAC}R$ , where R is the op amp feedback resistor. The direction of the DAC current will determine the polarity of the op amp output voltage.

FIGURE 2. CURRENT-TO-VOLTAGE CONVERTER CIRCUIT

#### The R-2R Ladder Network

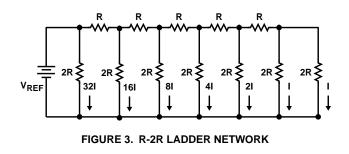

Intersil processes are not very good at making accurate resistors; the absolute tolerances may range from 0.5 to 30 percent depending on the how the resistor is made, it's value, where it is located on the die, and if it is trimmed. Intersil processes are extremely good at matching resistors, especially if the resistors are close in value such as is the case in a R-2R ladder network. The R-2R ladder relies on the matching for it's accuracy, and because Intersil processes match and track with a high degree of accuracy, many DACs rely on R-2R ladder networks. When an observer looks into any section of a R-2R ladder network they see a constant impedance R, so the switches and the other components which make up the DAC see a constant impedance. The branch currents in a R-2R ladder are binaurally weighted, see Figure 3, thus, when each branch contains a bit switch the bit currents will be binaurally weighted. R-2R ladder networks and their variations are commonly used to make DACs because of these advantages.

#### **Bipolar DACs**

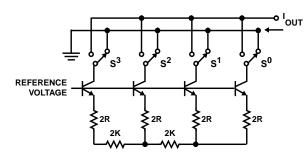

The two major classifications of DACs, bipolar and CMOS, are differentiated by the Intersil devices used to make them. Although they both perform the same function, their internal operation is different, making their strong points and weak points different.

FIGURE 4. BIPOLAR DAC WITH A R-2R LADDER

Bipolar junction transistors are used to make up the bipolar DAC. The general characteristics of a bipolar DAC are high speed, high output current, and high power drain. One of the simplest circuit configurations for a bipolar DAC is shown in Figure 4 where the R-2R ladder is combined with a reference, a series of current sources and bit switches to configure the DAC. Each transistor base is held at a constant voltage by the reference voltage, thus, if the transistors have a high current gain the emitter currents will be the same as the ladder branch currents. Effectively, the transistor's baseemitter junctions have been used to sense the branch currents, the ladder network functions as though the transistors didn't exist, and the bit switches direct the branch currents between the output and ground. It is not easy to make a bit switch with only bipolar transistors, so the range and resolution of early bipolar DACs was not very good. Bipolar DACs still exist because they are the fastest DACs in town.

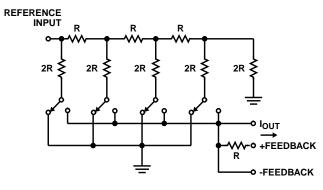

#### **CMOS DACs**

The schematic of a CMOS DAC is given in Figure 5. Notice that the CMOS DAC is nothing more than the R-2R ladder fabricated with bit switches to direct the branch currents. The CMOS transistors are used to make the bit switches; thin films such as nichrome are normally used to make the resistors. An extra resistor is bonded out and identified as "Feedback"; this resistor is meant to be used in a current to voltage converter circuit if a voltage output is desired. The branch currents in the ladder are added in the output per the settings of the bit switches. If no bit switches are set, as is shown in Figure 5, then the output current is zero. If all the bit switches are set, the output current will be one bit less than  $V_{REF}/R$ . The general equation for the DAC output current is given in Equation 9 (D is defined in Equation 6).

$$I_{OUT} = \left[V_{REF_{RE}}\right][D]$$

(EQ. 9)

### **DAC** Applications

Some applications, especially those requiring high speed, use the DAC current output directly. Normally the DAC gives the designer the option of grounding either one of two current outputs. This option enables the designer to select an increasing or decreasing output current as a function of an increasing digital input.

When a voltage output is required, the DAC output current is converted to voltage by summing it into the inverting input of an op amp as shown in Figure 2. The voltage configuration is always slower than the current configuration because the op amp must be compensated and has speed limitations. The "Feedback" shown in Figure 5 is normally used as the resistor shown in Figure 2; the internal resistor is used because it has the same drift and temperature coefficient as the ladder resisters. Using the internal resistor minimizes the drift from all causes, but if the designer has another reason, such as terminating a sensor correctly, a different value of R may be used. In these circumstances the designer must account for the circuit drift through other techniques.

Normally, the op amp compensation is accomplished through the use of an external capacitor placed in parallel with the feedback resistor. The output capacitance of the DAC causes op amp instability, and this capacitance value is dependent on the digital input, so the compensation capacitor must be selected for the highest DAC output capacitance. The addition of the feedback capacitor will form a compensated attenuator structure; see reference one for further compensation information.

The CMOS DAC can be used backwards with the reference voltage put into the DAC output, and the output taken from

the reference voltage input. This configures the DAC as a R-2R ladder voltage divider. Inverted DAC operation is employed when a positive voltage output is required and only a single power supply is available. The DAC sacrifices operating range in this mode; usually about 3 to 4 volts of overhead is required for the inverted DAC to operate correctly.

# **DAC Specifications**

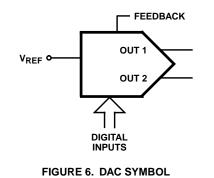

An ideal DAC transfer function is shown in Figure 7. Notice that each data points is discrete; they are not connected by a line. Although the data points are often represented by a line, this is just done for conceptual convenience. The ideal DAC transfer function starts at 0,0, and all of the data points fall on a theoretically straight line. The ideal DAC transfer function does not exist, but that is good because if it did exist somebody making a lot less money than us would be doing this work.

There are three major DAC error sources that always have to be corrected or accounted for. Two of these errors, offset

and gain, are DC errors, so they may be corrected rather easily with external components. Offset error is shown in Figure 8; this is just a DC offset similar to that seen in op amp design. It is corrected by summing in a reverse polarity voltage or current to cancel out the voltage or current causing the initial error. The gain error is similar to an op amp gain error caused by a resistor tolerance. It is corrected by placing a variable gain stage somewhere in the signal path.

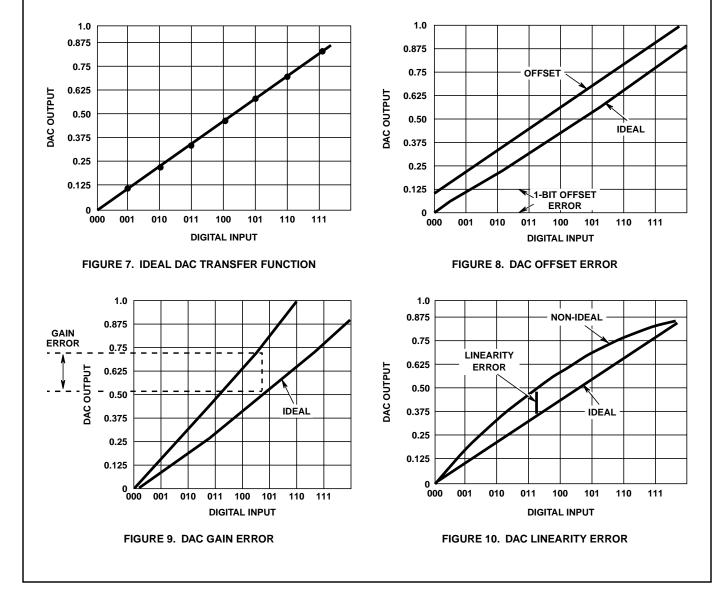

DAC linearity error comes in two flavors. First, we have integral nonlinearity, INL, which is the maximum deviation at any point of the output from it's theoretical straight line transfer function. Second, we have differential linearity error, DLE, which is the deviation from ideal at the transitions of adjacent codes. When the DLE exceeds 1 bit the DAC transfer function becomes non-monatomic, and this can cause instability or lock up, if the DAC is contained in a feedback loop.

There are other DAC error sources such as overshoot, settling time, etc., but these are minor compared to the major error sources.

### Typical Performance Curves

## Summary

The DAC converts a digital signal to an analog signal. It is the primary interface component between the digital system output and the analog system input. It can provide analog memory and multiplication while converting the digital signal into an analog signal. DACs come in two major flavors which are bipolar or CMOS, and these two names are derived from the type of transistors used to manufacture the DAC. A bipolar DAC is usually faster than a CMOS DAC, but it generally consumes more power. The equation for a DAC is  $I_{OUT} = (V_{REF}/R)D$ . The major error sources in a DAC are offset, gain, and linearity.

### Reference

For Intersil documents available on the web, see http://www..intersil.com/

Intersil AnswerFAX (321) 724-7800.

1. Mancini, Ron, *"Feedback, Op Amps and Compensation"*, Intersil, AnswerFAX Doc. No. 99415.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com